Step-by-Step

[Memory] DRAM 본문

DRAM

Dynamic Random Access Memory

| Dynamic | DRAM은 데이터를 Capacity (전하를 저장하는 가장 작은 축적기) 에 저장한다. 이 Capacity는 시간이 지나면 전하가 자연스럽게 방전되기 때문에, 저장된 정보가 금방 사라진다. 주기적으로 데이터를 다시 충전해주는 Refresh 동작이 필요한데, 즉, Dynamic은 저장 상태가 계속 유지되지 않고, 끊임없이 갱신해야 한다는 의미이다. |

| Random Access | 메모리에 저장된 데이터는 순차적으로 접근하는 것이 아니라, 원하는 주소로 바로 접근할 수 있다. |

| Memory | DRAM은 데이터를 저장하는 장치로, 휘발성 메모리에 속하여 전원이 꺼지면 데이터가 사라진다. 주로 CPU와 보조 저장장치(SSD / HDD) 사이에서 중간 역할을 하며, 프로그램 실행 중 필요한 데이터를 일시적으로 저장한다. |

DRAM의 Refresh

- DRAM의 Refresh 작업은 메모리 컨트롤러(MC)에서 자동으로 담당한다.

- DRAM의 Cell Capacitor가 일정 시간이 지나면 전하가 날아가기 때문에, 컨트롤러가 주기적으로 셀을 읽고 다시 써서 전하를 보충한다.

- 보통 수 밀리초(ms) 단위로 모든 셀을 한 번씩 refresh 한다. (보통 64ms ~ 128ms)

※ Refresh 작업은 왜 ms 단위로 해야할까?

1. Capacitor 의 크기

DRAM의 셀 하나는 트랜지스터 1개 + 캐패시터 1개로 구성되는데, 이 캐패시터가 나노미터 크기로 매우 작다.

저장할 수 있는 전하량이 극히 적어, 새어 나가면 0과 1의 경계가 모호해진다.

2. 누설 전류

반도체 내부는 완벽한 절연체가 없어서, 시간이 지나면 전하가 조금씩 빠져나가게 된다.

미세 공정일수록 누설 전류가 커지기 때문에 더 자주 refresh가 필요하다.

3. 온도

온도가 높을수록 전자가 빨리 이동하므로, 고온에서는 refresh 주기를 더 짧게 잡아야 한다.

반도체 물질은 온도가 높아지면 전자들의 에너지가 커져서 쉽게 이동할 수 있고, 전자가 장벽을 넘어가는 확률이 높아져 전하가 더 빨리 새어나가게 된다.

DRAM의 구조

DRAM의 최소 단위는 1bit Cell로, 트랜지스터와 커패시터로 구성되어 있다.

- 트랜지스터 (Transistor) : 스위치 역할로, 데이터 읽기 / 쓰기를 제어한다.

- 커패시터 (Capacitor) ; 전하를 저장해서 데이터를 유지한다. (전하가 있으면 1, 없으면 0)

[Bit Cell]

┌──────┐

│ C │ ← 커패시터 (데이터 저장)

└──┬───┘

│

T ← 트랜지스터 (액세스 제어)

│

Word Line → 셀 선택

DRAM의 배열 구조

DRAM은 수많은 bit Cell을 행(Row) x 열(Column) 로 배열한 매트릭스 구조를 가진다.

- Word Line (행 선택선) : 특정 행을 선택한다.

- Bit Line (열 데이터선) : 선택된 셀의 데이터를 읽거나 쓴다.

- Row Decoder : 입력된 주소의 행 번호를 해석해서 Word Line을 활성화한다. (해당 Bit line 연결을 위한 활성화)

- Column Decoder : 선택된 행에서 읽고자 하는 열을 선택한다.

DRAM의 channel

CPU (또는 메모리 컨트롤러)와 DRAM 모듈 사이의 데이터 통로를 의미한다.

Channel이 많으면 한 번에 더 많은 데이터를 동시에 전송할 수 있어서, 메모리 대역폭(bandwidth)이 증가한다.

※ Memory 대역폭(Bandwidth)의 의미는?

CPU(혹은 다른 Master)와 메모리 간 일정 시간 동안 전송할 수 있는 데이터의 양

- 단위 : 보통 GB/s

- 계산 방법 : 대역폭 = 메모리 클럭 속도 x 데이터 전송 수 x 버스 폭 x 채널 수

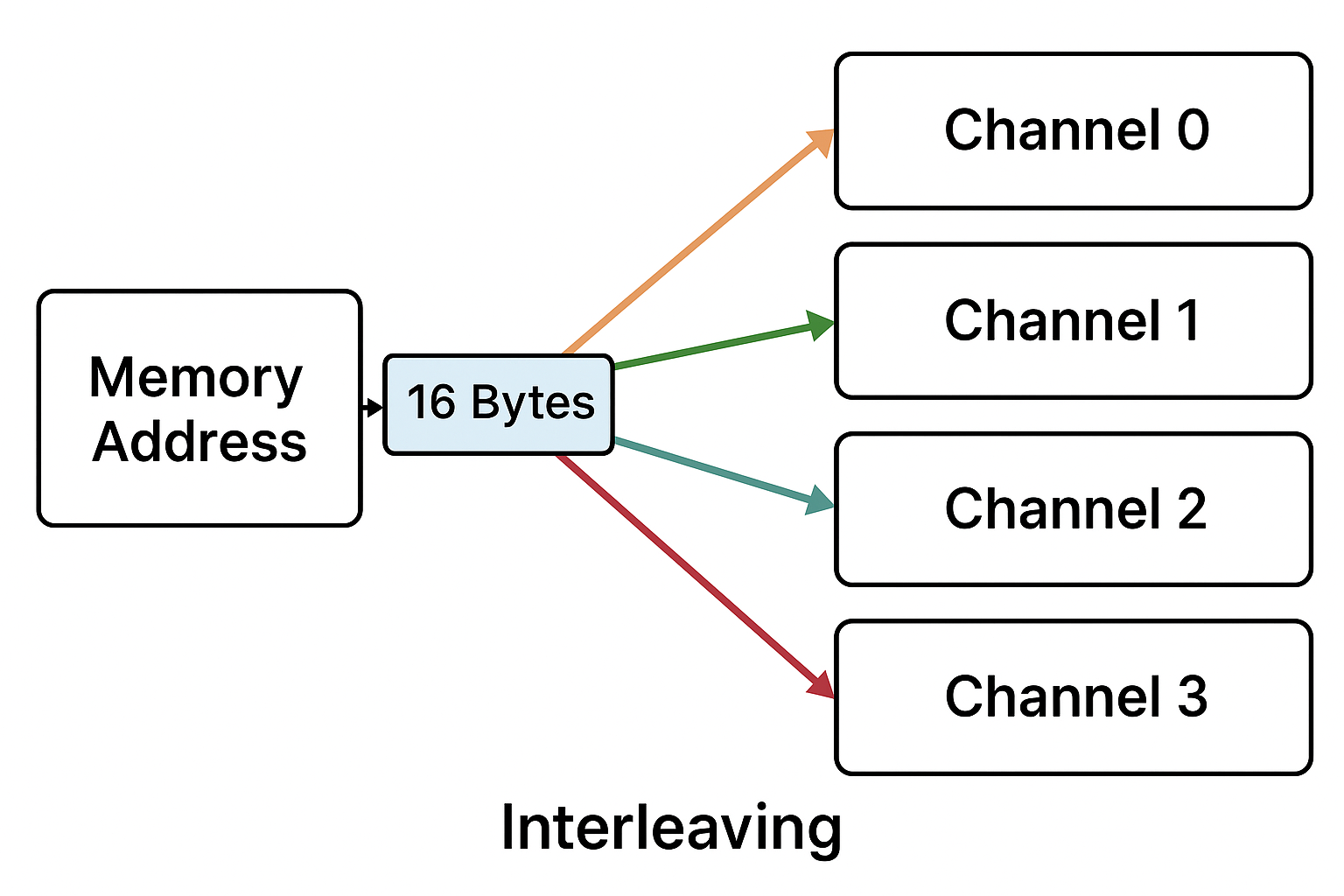

Channel의 Interleaving

여러 메모리 채널을 번갈아 사용하여 데이터 접근 병목을 줄이는 기법이다.

- 단순히 한 채널만 사용하면 CPU가 메모리를 기다려야하는 시간이 생길 수 있다.

- Interleaving을 사용하면 여러 채널이 병렬로 동작하면서 CPU가 대기하는 시간을 줄일 수 있다.

- channel이 담당하는 DRAM의 물리적인 주소 값은 고정이나, 연속적인 주소값은 아니다. (연속적인 주소들이 다른 채널로 번갈아 분산될 수 있다.)

ChatGPT의 말:

네, 질문하신 상황을 정리하면 이렇게 이해할 수 있습니다. 하나씩 단계별로 풀어볼게요.

상황 요약

- CPU가 16바이트를 요청.

- DRAM 프로토콜 전송 폭이 128비트(=16바이트).

- DRAM 채널이 4개 있고, interleaving 되어 있음.

즉, 16바이트를 한 번에 전송할 수 있는 폭은 128비트 → 정확히 16바이트인데, 채널 4개에 interleaving 되어 있기 때문에 데이터를 4개 채널에 분산해서 저장/전송함.

Interleaving 구조

- 예를 들어, 16바이트 데이터를 4바이트 단위로 나눠서 채널에 배분했다고 가정합니다.

| CH0 | D0~D3 |

| CH1 | D4~D7 |

| CH2 | D8~D11 |

| CH3 | D12~D15 |

- CPU가 16바이트를 요청하면 각 채널에서 4바이트씩 동시에 읽음 → 총 16바이트 완성.

- 즉, interleaving 덕분에 병렬로 데이터 읽기 가능 → 메모리 대역폭 향상.

최종 전달 과정

- CPU 요청 → 메모리 컨트롤러가 16바이트 주소를 4채널로 분배.

- 각 채널에서 **각각 데이터 일부(예: 4바이트)**를 DRAM에서 읽음.

- 메모리 컨트롤러에서 4채널 데이터를 조합하여 16바이트 완성.

- 완성된 16바이트를 CPU로 전달.

✅ 정리하면:

네, 각 채널에서 데이터를 가져와 메모리 컨트롤러가 조합한 뒤 CPU에 전달합니다.

Interleaving은 한 번에 여러 채널에서 병렬로 데이터를 읽어 전체 전송 시간을 줄이는 기술입니다.